数字集成电路设计 从理论到实践的创新之路

数字集成电路(Digital Integrated Circuit,简称DIC)是现代电子系统的核心,其设计是连接抽象逻辑与物理实现的关键桥梁。《数字集成电路设计》这门课程,系统性地阐述了从高层次描述到硅片成品的完整流程,是微电子与半导体领域人才培养的基石。

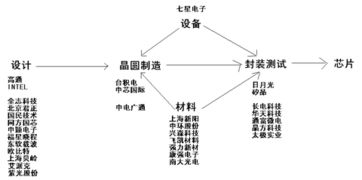

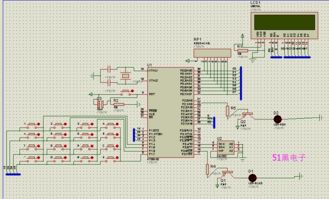

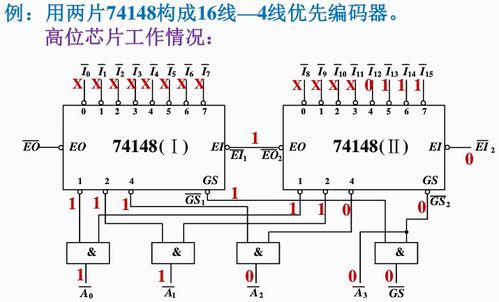

课件通常以“集成电路设计”为开篇,强调其在信息时代的基础性地位。设计流程始于设计规范与架构定义,明确芯片的功能、性能与功耗目标。设计人员使用硬件描述语言(如VHDL或Verilog)进行寄存器传输级(RTL)设计,将算法和行为转化为可综合的逻辑电路描述。这是创造性的核心阶段,决定了电路的逻辑正确性和初步效率。

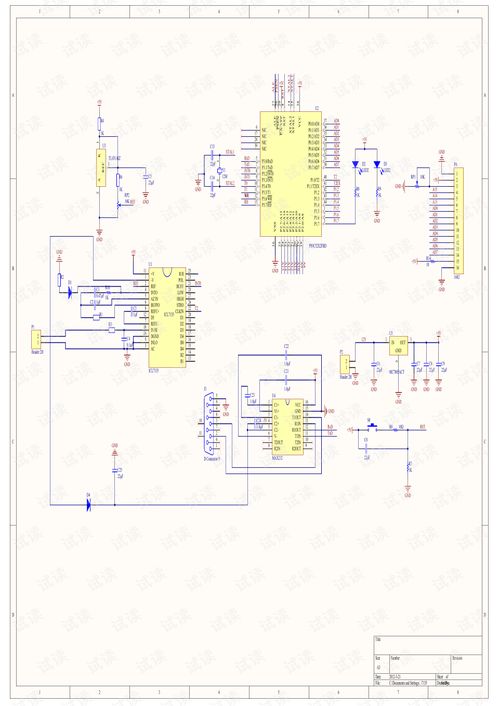

逻辑综合是将RTL代码映射到特定工艺库标准单元的过程,生成门级网表。此时,静态时序分析(STA)至关重要,用于验证电路在给定时序约束下能否正确工作。之后进入物理设计阶段,包括布局规划、单元布局、时钟树综合、布线等步骤,将逻辑网表转化为具体的几何图形(版图),同时需反复进行时序、功耗和信号完整性的分析与优化。

验证贯穿始终,包括功能验证、形式验证以及后仿真的时序验证,确保设计在制造前万无一失。生成的GDSII格式版图文件交付晶圆厂进行流片制造。

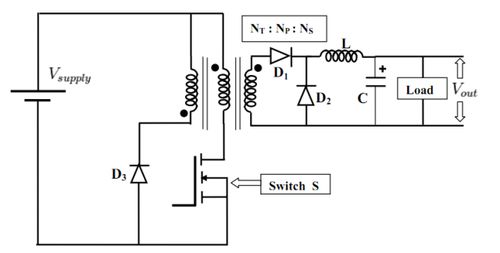

当前,数字集成电路设计正面临工艺节点微缩带来的功耗、时序收敛和物理效应等巨大挑战。低功耗设计技术、可测性设计(DFT)以及基于先进工艺(如FinFET)的设计方法成为课件中日益重要的内容。高层次综合(HLS)、基于平台的模块化设计以及人工智能在EDA工具中的应用,正在重塑设计方法论,提升设计自动化水平和效率。

掌握《数字集成电路设计》的知识体系,意味着不仅理解了从行为到版图的转换链条,更把握了驱动计算、通信、人工智能等一切数字时代进步的底层硬件创新逻辑。这门课程及其课件,是工程师将创新思想转化为切实芯片产品的路线图与工具箱。

如若转载,请注明出处:http://www.58qds.com/product/27.html

更新时间:2026-04-22 22:47:45