集成电路设计中保护电路的设计要点与注意事项

在集成电路设计中,保护电路是确保芯片在各种异常条件下安全、可靠运行的关键模块。一个设计不当的保护电路可能导致芯片性能下降、功能失效,甚至永久性损坏。以下是设计保护电路时需要重点关注的几个要点,设计人员务必予以高度重视。

1. 明确保护目标与异常条件

设计之初,必须清晰界定需要防护的异常情况,例如电源过压、欠压、浪涌、静电放电(ESD)、闩锁效应(Latch-up)、过流以及过热等。不同的应用场景(如汽车电子、工业控制、消费电子)对保护的要求和等级差异巨大,需根据具体规范(如AEC-Q100、JEDEC标准)确定测试条件和耐受水平。

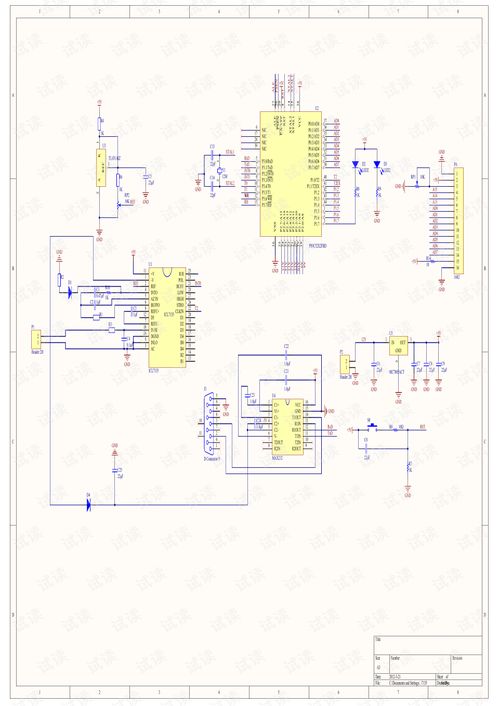

2. ESD保护电路的设计与布局

静电放电是芯片在制造、组装和使用中最常见的威胁。ESD保护电路通常位于芯片的输入/输出(I/O)焊盘和电源焊盘附近,其核心是在瞬间高压到来时提供一条低阻抗的泄放路径,将电流导向电源或地线,从而保护内部核心电路。设计时需注意:

- 选择合适的ESD保护器件结构,如二极管、栅接地NMOS(GGNMOS)、硅控整流器(SCR)等,权衡其触发电压、维持电流、面积和寄生电容对信号完整性的影响。

- 确保ESD保护器件到被保护电路及到电源/地网络的布线路径尽可能短而宽,以降低寄生电阻和电感,避免保护失效。

- 进行完整的ESD仿真与测试,确保符合HBM(人体模型)、CDM(充电器件模型)、MM(机器模型)等标准要求。

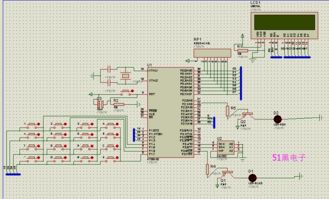

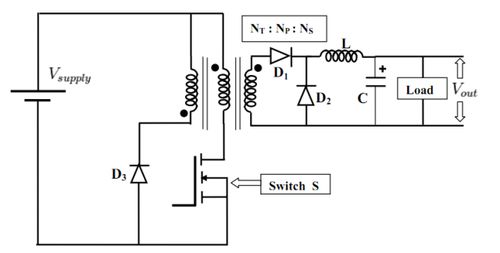

3. 电源管理:过压与欠压保护(OVP/UVP)

电源电压的异常波动会直接导致电路功能错误或器件击穿。过压保护电路通常通过电压检测模块(如电阻分压网络与比较器)监控电源电压,一旦超过阈值,即触发关断或钳位动作。欠压保护则在电压过低、可能导致逻辑状态混乱时,使芯片进入安全复位状态。要点包括:

- 设置合理的电压阈值和迟滞(Hysteresis),防止在阈值附近因噪声频繁触发。

- 保护电路的响应速度必须快于异常电压的变化速度,通常要求纳秒级响应。

- 保护电路自身的功耗要低,尤其在电池供电设备中,不应显著影响待机时间。

4. 过流与过热保护

当电路发生短路或超负荷运行时,可能因电流过大导致局部过热和金属连线熔断。过流保护通过检测电流(如使用感应电阻或镜像晶体管),并与参考值比较,一旦超标则限流或关断。过热保护则利用温度传感器(如带隙基准中的PN结)检测结温,超过安全范围(通常125°C~150°C)即触发热关断。设计时需确保:

- 保护阈值精确且受工艺角(Process Corner)和温度变化的影响小。

- 过热保护应具备自恢复或手动复位功能,并避免在临界温度附近振荡。

- 功率器件(如功率MOSFET)的布局需均匀,避免热点(Hot Spot)导致传感器检测失灵。

5. 防止闩锁效应(Latch-up)

闩锁效应是由寄生PNPN结构触发的低阻抗通路,可能导致大电流烧毁芯片。预防措施包括:

- 在版图设计中,对PMOS和NMOS器件使用足够的保护环(Guard Ring),即掺杂物形成的环,以收集少数载流子,降低寄生三极管的增益。

- 确保电源和地焊盘布局合理,降低衬底和阱的寄生电阻。

- 遵循设计规则,保持器件间足够的间距。

6. 保护电路的可靠性与鲁棒性验证

保护电路本身必须在最恶劣的工艺、电压和温度(PVT)条件下可靠工作。因此,需要进行全面的后仿真(Post-layout Simulation),包括瞬态仿真、蒙特卡洛(Monte Carlo)分析以评估工艺偏差的影响,以及电热协同仿真。流片后,必须进行严格的可靠性测试,如HTOL(高温工作寿命)、ESD测试、闩锁测试等。

7. 系统级协同考虑

芯片保护电路需与系统级保护(如保险丝、TVS二极管、热敏电阻)协同设计。例如,片内ESD保护应对HBM级别的放电,而系统级TVS管则负责防护更高能量的浪涌。清晰界定芯片与板级保护的职责范围,可以优化整体成本与性能。

保护电路设计是集成电路设计中一项关乎芯片“生存”的关键任务。它要求设计者不仅深入理解器件物理、电路原理和版图艺术,还必须具备系统思维和严谨的验证习惯。忽略任何一个细节,都可能使精心设计的功能电路毁于一旦。因此,在项目规划中,务必为保护电路的设计、仿真与测试分配足够的时间与资源,真正做到防患于未然。

如若转载,请注明出处:http://www.58qds.com/product/19.html

更新时间:2026-05-06 14:29:30