FPGA板级电路设计五要素详解

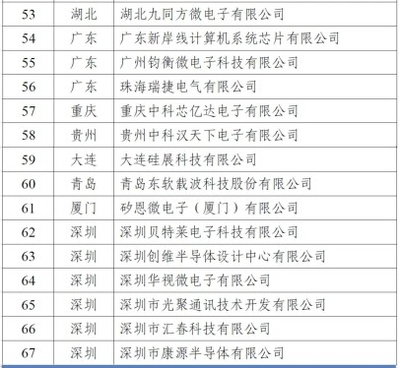

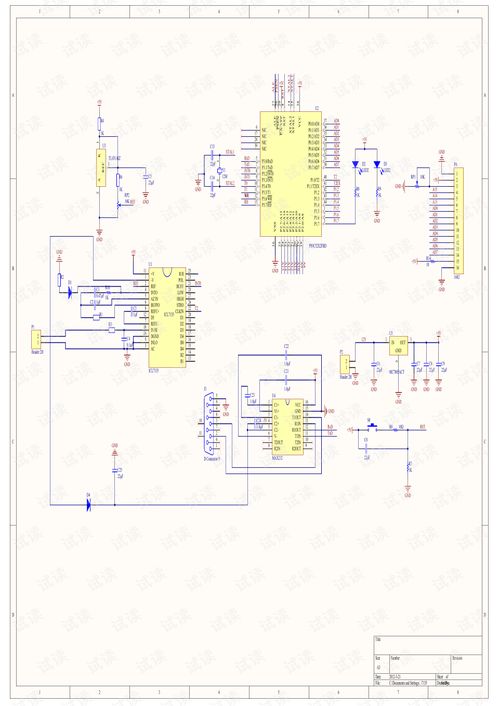

在FPGA/CPLD/DSP等数字系统的开发过程中,板级电路设计是连接芯片与应用系统的关键桥梁。一个稳健、可靠的板级设计是项目成功的基础。本文将结合OpenEDV开源电子网及集成电路设计社区的实践经验,系统阐述FPGA板级电路设计的五个核心要素。

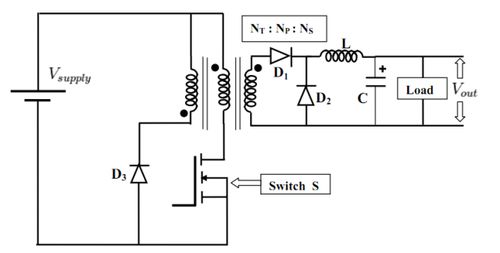

要素一:电源完整性设计

电源是系统的心脏。FPGA通常需要内核电压、辅助电压和多个Bank的I/O电压,设计时必须考虑:

- 电源树规划:明确各电压的上下电顺序要求,采用PMU或专用时序控制器确保顺序。

- 电源噪声抑制:在芯片电源引脚附近放置去耦电容,采用多层板并规划完整的电源地平面,以提供低阻抗回流路径。

- 电流容量与散热:准确估算各电源轨的最大电流,留足余量,并考虑大电流路径的走线宽度与散热措施。

要素二:时钟与复位电路设计

时钟与复位是系统的脉搏与起点。

- 时钟电路:为获得低抖动、稳定的时钟,推荐使用晶体振荡器模块。时钟线应作为特征阻抗受控的传输线处理,远离噪声源,并尽量短。对于高速全局时钟,需使用FPGA的专用时钟输入引脚和全局时钟网络。

- 复位电路:确保上电复位信号干净、无毛刺。通常采用阻容延时电路或专用复位芯片,产生满足FPGA要求的最小复位脉宽。异步复位、同步释放是推荐的设计模式。

要素三:配置电路设计

FPGA在上电后需要加载配置数据。设计需关注:

- 配置模式选择:根据应用需求(如是否要求加密、速度、主从关系)选择JTAG、SPI Active、SPI Passive等模式。

- 配置存储器:如使用SPI Flash,应将其靠近FPGA放置,数据线等长处理,并注意上拉/下拉电阻的正确配置以满足不同阶段的电平要求。

- JTAG接口:作为调试和编程的必备通道,应预留标准的JTAG接头,信号线上可串联小电阻以阻尼反射。

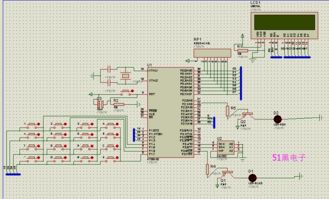

要素四:I/O接口与信号完整性

FPGA的强大之处在于其灵活的可编程I/O。

- Bank划分与电平标准:仔细查阅手册,将相同电压和电平标准(如LVCMOS、LVDS)的信号分配到同一I/O Bank,严禁超压。

- 阻抗匹配与端接:对于高速信号(如DDR、千兆以太网),必须进行阻抗匹配(通常50Ω单端,100Ω差分)。根据拓扑结构使用源端串联、并联或戴维宁端接等方式,并严格控制差分对等长、间距。

- 未用引脚处理:将未用引脚设置为三态或弱上拉,避免悬空引入噪声或增加功耗。

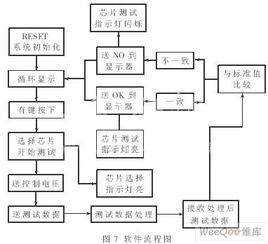

要素五:调试与测试设计

“设计是为了调试”,在板级设计阶段就应预留观测和测试点。

- 测试点:在关键电源、复位、配置状态信号和重要用户I/O上放置测试点,方便示波器和逻辑分析仪探测。

- LED指示灯:简单的电源指示灯、配置完成指示灯、心跳灯等,能极大提升调试效率。

- 扩展接口:可预留一些通用的扩展接口(如PMOD、高速连接器),方便功能验证和未来升级。

FPGA板级电路设计是一项系统工程,需要统筹考虑电源、时钟、配置、I/O和调试五大要素。严谨的原理图设计、符合信号完整性要求的PCB布局布线,以及充分的预仿真,是保障一次成功的关键。OpenEDV等开源社区汇集了大量实践案例与经验分享,深入参与其中,与同行交流,能有效规避常见陷阱,提升设计质量。从芯片到稳定运行的系统,优秀的板级设计正是这其中的坚实基石。

如若转载,请注明出处:http://www.58qds.com/product/15.html

更新时间:2026-05-06 17:38:42