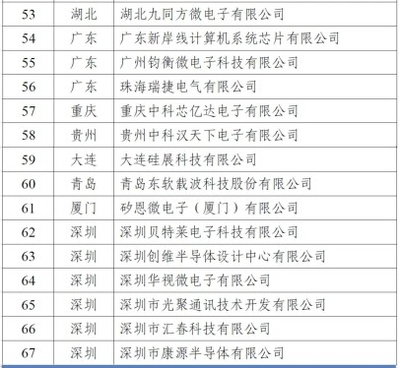

nRF52832开发板电路方案设计与原理图解析

引言

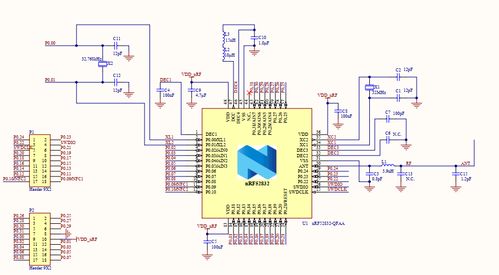

随着物联网(IoT)和可穿戴设备的快速发展,低功耗蓝牙(BLE)技术已成为无线连接的核心。Nordic Semiconductor的nRF52832系统级芯片(SoC)以其优异的射频性能、超低功耗和丰富的外设接口,成为众多嵌入式开发项目的首选。设计一款基于nRF52832的开发板,不仅需要深刻理解芯片本身,还需在电路方案、原理图设计和集成电路布局上精益求精,以确保其稳定性、可靠性和易于开发。本文将系统阐述nRF52832开发板的电路方案设计要点与原理图核心部分解析。

一、核心电路方案设计

一个完整的nRF52832开发板电路方案通常包含以下几个核心子系统:

- 核心供电与电源管理电路:

- 电源输入:设计需支持多种供电方式,如USB 5V输入、外部3.3V直流输入以及纽扣电池(CR2032等)输入。关键是需要使用低压差线性稳压器(LDO),如MIC5205或TLV70033,将输入电压稳定至nRF52832所需的核心电压(通常为1.8V至3.6V,典型3.3V)。

- 去耦与滤波:在VDD引脚附近放置充足且容值匹配的去耦电容(如100nF MLCC紧贴引脚,并联10uF钽电容),是抑制电源噪声、保证芯片稳定运行的基础。射频电源引脚(VDDH)需要更严格的滤波,常采用π型滤波器(电感+电容)。

- 功耗管理:为充分发挥芯片超低功耗特性,电路设计应便于测量不同模式下的电流消耗,可预留零欧姆电阻或测试点。

- 时钟电路:

- 高频晶体振荡器(HFXO):用于提供射频和高性能外设所需的精准时钟。必须严格按照nRF52832数据手册要求,选择负载电容匹配的32MHz晶体(如FA-20H),并紧贴芯片XL1/XL2引脚布局,接地包围以减少干扰。

- 低频晶体振荡器(LFXO):为实时时钟(RTC)和低功耗睡眠模式提供32.768kHz时钟,是实现超低功耗待机的关键。同样需注意负载电容和布局。

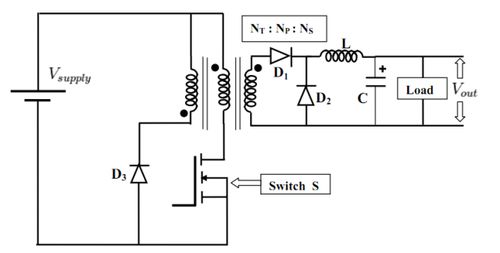

- 射频(RF)电路:

- 这是设计成败的关键。nRF52832采用单端射频输出,需要通过巴伦(Balun)电路转换为差分信号,再连接至天线。通常采用集成巴伦滤波器(如BALF-NRF02D3)或分立LC网络方案。集成方案性能更优、布局更简单,是首选。

- 天线选择与匹配:根据应用场景选择PCB天线(如倒F天线)、陶瓷天线或外接天线。必须设计π型匹配网络(通常为电容/电感),并预留调试点位,通过矢量网络分析仪(VNA)进行阻抗匹配(目标50欧姆),以优化射频性能。

- 调试与编程接口:

- SWD接口:标准的2线Serial Wire Debug接口(SWDIO, SWCLK),配合RESET引脚,是连接J-Link等调试器进行程序下载和调试的必备通道。需预留标准的10针1.27mm间距连接器或测试点。

- 串口(UART):通过nRF52832的UART引脚连接USB转串口芯片(如CP2102、CH340),提供便捷的日志打印和通信功能,是开发调试的重要辅助。

- 外设与扩展接口:

- 将芯片未使用的GPIO、ADC、I2C、SPI、PWM等引脚通过排针或测试点引出,方便用户连接传感器、显示屏等外围模块。

- 可集成常用外设,如用户按键、LED指示灯、温湿度传感器等,构成最小功能验证系统。

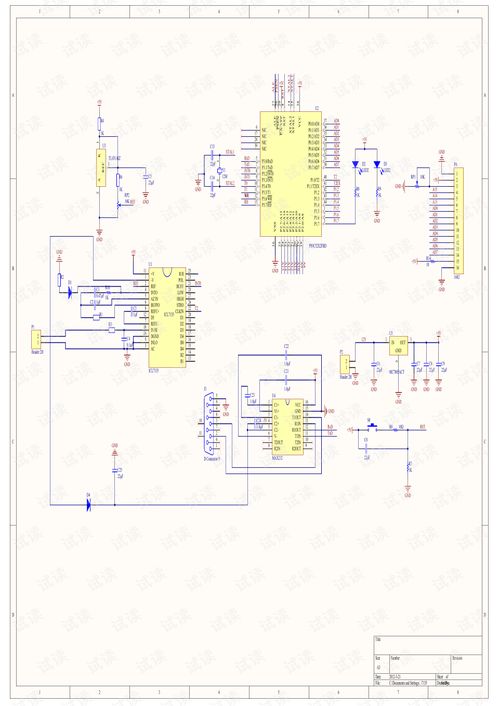

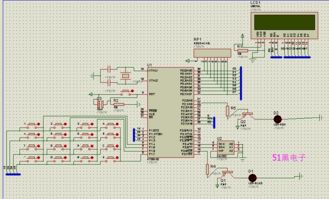

二、原理图设计详解与集成电路考量

在将上述方案转化为原理图时,需遵循模块化、清晰化的原则。

- 原理图模块划分:建议将原理图分为:电源模块、nRF52832核心及外围电路、时钟电路、射频前端电路、调试编程接口、外设接口与扩展、用户交互(按键/LED)等几个部分。这有助于检查和团队协作。

- 关键部分原理图要点:

- nRF52832符号绘制:应正确区分模拟电源(VDD)、数字电源(VDD)、射频电源(VDDH)、接地(VSS)以及模拟/数字接地。所有电源引脚必须连接,不可悬空。

- 复位电路:通常采用RC上电复位电路(如10k上拉电阻+100nF电容到地),并预留手动复位按钮。RESET引脚内部有上拉,外部电路需简洁。

- 射频原理图:若使用集成巴伦滤波器,其连接应严格参照数据手册。天线端口可增加ESD保护器件。匹配网络元件的值需根据实际PCB和天线在调试中确定,原理图上可标注为“待调”。

- 集成电路(IC)设计思维:虽然开发板主要进行板级设计,但需具备IC设计层面的考量:

- 信号完整性:高速数字信号(如SWD)和模拟射频信号路径应尽量短直,避免过孔,远离噪声源。

- 电源完整性:建立稳固的电源分配网络(PDN),确保电源平面低阻抗,为瞬间大电流提供通路。

- 热设计:nRF52832功耗虽低,但大功率射频发射时仍会产生热量,需保证适当铜箔散热,避免热岛效应。

- ESD与保护:在USB数据线、天线接口、用户按键等对外端口,应考虑添加TVS管、稳压二极管等保护器件,提升板卡鲁棒性。

三、PCB布局与布线建议

原理图完成后,PCB布局布线是实现电气性能的物理保障。

- 层叠结构:至少使用4层板(顶层-信号/元件, 内层1-地平面, 内层2-电源平面, 底层-信号/元件),为关键信号提供完整的回流路径。

- 布局顺序:优先放置nRF52832芯片、两个晶体、巴伦/射频匹配网络、天线接口,确保它们处于最紧凑、干扰最小的区域。然后是电源芯片、去耦电容、调试接口,最后是扩展排针。

- 射频部分布局:这是布局的重中之重。需做到:

- 射频路径(从芯片RF引脚到天线)最短。

- 用地过孔墙严格隔离射频区域与其他数字区域。

- 射频路径下方所有层保持完整地平面,不得走线。

- 匹配元件对称紧挨放置。

- 电源布线:采用星型拓扑或平面分割,避免数字噪声通过电源串扰至模拟/射频部分。电源线宽足够,以满足电流需求。

##

设计一款高性能的nRF52832开发板,是一个系统工程,涵盖了从芯片选型、电路方案制定、详细原理图设计到PCB实现的完整链条。其中,严谨的电源与时钟设计是基石,卓越的射频电路布局是灵魂,而良好的扩展性与调试支持则是其作为开发工具的价值体现。在设计中贯穿集成电路的思维,关注信号与电源完整性,方能打造出稳定可靠、便于二次开发的硬件平台,为后续的嵌入式软件开发与产品化奠定坚实基础。开发者应在实践中不断迭代优化,并借助频谱仪、网络分析仪等工具进行测试验证,以确保设计达到预期性能指标。

如若转载,请注明出处:http://www.58qds.com/product/14.html

更新时间:2026-05-06 04:46:49