集成电路设计 从“配料”到“原材料”的计算艺术

集成电路(IC)设计常被比作一场精密绝伦的数字烹饪。如果说最终流片生产的物理芯片是美味佳肴,那么设计阶段的核心工作之一,便是进行精准的“配料”与“原材料”计算。这并非指物理的硅片或金属材料,而是指构成芯片功能与性能的一系列抽象“原料”——逻辑门、晶体管、存储单元、互连线等资源及其背后的功耗、时序与面积预算。

一、 “配料计算”:功能单元的量化配比

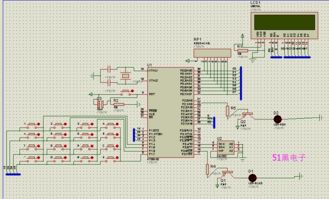

在芯片架构规划与前端设计阶段,“配料计算”主要指对各种功能模块所需资源量的估算与分配。

- 核心“食材”——逻辑资源:设计师根据目标功能(如CPU核心、图像处理器、通信接口),将其分解为寄存器、加法器、乘法器、多路选择器等基本逻辑单元。通过高层次综合(HLS)或RTL代码描述,工具可以初步估算出实现该功能大致需要多少等效门(Gate Count)或查找表(LUT,针对FPGA)。这好比根据菜谱计算需要多少主料。

- 关键“调味”——存储资源:现代芯片离不开缓存(Cache)、寄存器堆、片上内存(SRAM)。其容量与结构(如几路组相连)需经过精密计算,在访问速度、芯片面积和功耗之间取得平衡。计算不足会导致性能瓶颈,过量则会无谓增加成本和功耗。

- “特殊配料”——IP核与接口:许多设计会集成成熟的第三方IP核(如处理器内核、高速串行接口)。它们作为预制的“料理包”,其资源占用(门数、引脚数)是明确的,需要提前计入总预算。

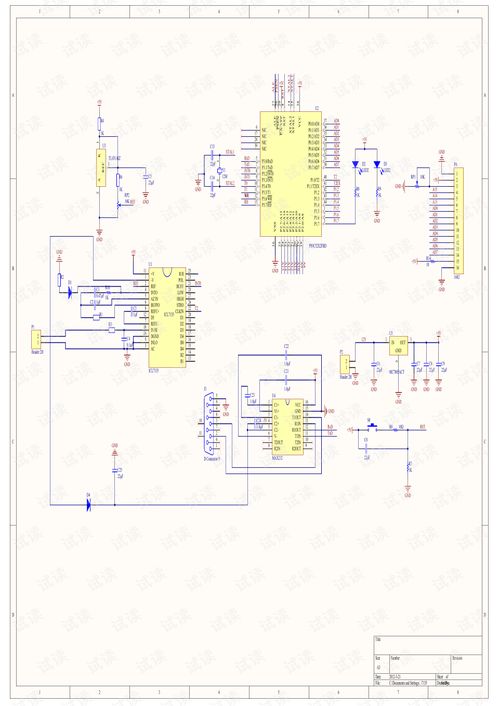

二、 “原材料计算”:物理实现的约束与优化

进入后端物理设计阶段,抽象的“配料”将映射到实际的物理“原材料”上,计算更加具体且与制造工艺紧密相关。

- 面积计算:这是最直观的“原材料”计算。综合与布局布线工具会根据设计网表、标准单元库和工艺节点(如7nm、5nm),计算出芯片核心(Core)的预估面积。面积直接关联成本(每片晶圆能切割出的芯片数)。设计师需要通过优化算法、复用逻辑、压缩内存来“精打细算”。

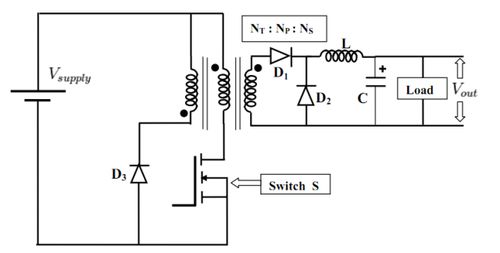

- 功耗计算:功耗是另一项关键“原料”预算,分为静态功耗和动态功耗。

- 动态功耗 与时钟频率、电路翻转活性、电压平方成正比。需要通过门控时钟、电压频率调节(DVFS)、优化数据路径等技术来“节流”。

- 静态功耗(主要是漏电)在先进工艺下尤为突出,与晶体管数量、温度及工艺特性相关。

设计早期需建立功耗预算模型,并在整个流程中使用工具进行功耗分析,确保不超出封装散热和电池续航的“供应上限”。

- 时序计算:确保信号在要求的时间窗口内稳定传输是芯片正常工作的基础。这涉及对时钟树网络、组合逻辑路径延迟的精确计算。建立时间(Setup Time)和保持时间(Hold Time)的违例必须通过调整电路、插入缓冲器、优化布局等手段解决,可以看作是“原材料”加工时间的精准调度。

- 互连线资源计算:在纳米级工艺下,互连线的电阻电容效应(RC Delay)已成为影响性能和功耗的主导因素之一。后端工具需要计算并优化金属层的布线资源,避免拥塞,同时控制信号完整性问题(如串扰)。

三、 计算工具与方法:设计师的“智能厨房”

现代集成电路设计已离不开强大的电子设计自动化(EDA)工具链,它们构成了进行上述计算的“智能厨房”。

- 架构探索工具:在早期进行高性能建模和资源预估。

- 综合工具:将RTL代码“编译”为门级网表,并给出初步的面积、时序报告。

- 静态时序分析(STA)工具:对时序路径进行 exhaustive 的验证计算。

- 功耗分析工具:基于仿真数据或统计模型进行功耗计算。

- 物理实现工具:完成布局、时钟树综合、布线与寄生参数提取,提供最终的面积、时序、功耗签核数据。

###

集成电路设计中的“配料”与“原材料”计算,是一个贯穿始终、层层递进、不断迭代优化的过程。它融合了系统架构的创造性规划与物理实现的严谨约束。优秀的芯片设计师,如同一位技艺高超的总厨,不仅需要深谙各种“食材”(电路架构)的特性,更要精通“厨房”(EDA工具)里的每一种计量工具,才能在有限的“成本预算”(面积、功耗、时序)内,烹制出功能强大、能效卓越的“芯片盛宴”。随着工艺演进至3nm乃至更小节点,这种计算的复杂性与精确性要求只会越来越高,持续驱动着设计方法和工具的革新。

如若转载,请注明出处:http://www.58qds.com/product/12.html

更新时间:2026-04-22 11:28:48